W9412G6KH-5Your current position:Home > W9412G6KH-5

W9412G6KH-5

Description

W9412G6KH is a CMOS Double Data Rate synchronous dynamic random access memory (DDR SDRAM); organized as 2M words* 4 banks * 16 bits. W9412G6KH delivers a data bandwidth of up to 400M words per second. To fully comply with the personal computer industrial standard, W9412G6KH is sorted into the following speed grades: -5, -5I and -6I. The -5/-5I grades are compliant to the DDR400/CL3 specification (the -5I industrial grade which is guaranteed to support -40°C ≤ TA ≤ 85°C). The -6I industrial grade is compliant to the DDR333/CL3 specification which is guaranteed to support -40°C ≤ TA ≤ 85°C. All Inputs reference to the positive edge of CLK (except for DQ, DM and CKE). The timing reference point for the differential clock is when the CLK and CLK signals cross during a transition. Write and Read data are synchronized with the both edges of DQS (Data Strobe). By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9412G6KH is ideal for any high performance applications.

Feature

2.5V ± 0.2V Power Supply for DDR400/333

Up to 200 MHz Clock Frequency Double Data Rate architecture; two data transfers per clock cycle

Differential clock inputs (CLK and CLK )

DQS is edge-aligned with data for Read; center-aligned with data for Write

CAS Latency: 2, 2.5 and 3

Burst Length: 2, 4 and 8

Auto Refresh and Self Refresh

Precharged Power Down and Active Power Down Write Data Mask

Write Latency = 1

15.6µS Refresh interval (4K/64 mS Refresh)

Maximum burst refresh cycle: 8

Interface: SSTL_2

Packaged in TSOP II 66-pin, using Lead free materials with RoHS compliant

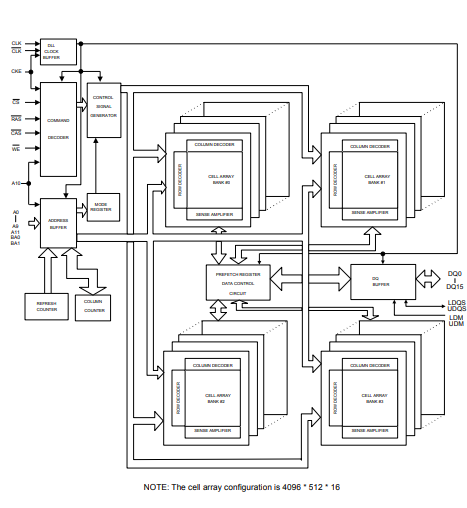

Block diagram

W9412G6KH-5

描述

W9412G6KH是CMOS双数据速率同步动态随机存取存储器(DDR SDRAM);组织为2M字* 4行* 16位。W9412G6KH提供高达每秒400M字的数据带宽。为了完全符合个人电脑行业标准,W9412G6KH分为以下速度等级:-5,-5I和-6I。-5/-5I等级符合DDR400/CL3规范(-5I工业级,保证支持-40°C≤TA≤85°C)。-6I工业级符合DDR333/CL3规范,保证支持-40°C≤TA≤85°C。所有输入均参考CLK的正边(DQ, DM和CKE除外)。差分时钟的计时参考点是当CLK和CLK信号在转换过程中交叉时。写入和读取数据与DQS(数据频闪)的两边同步。通过具有可编程模式寄存器,系统可以改变突发长度、延迟周期、交织或顺序突发以最大化其性能。W9412G6KH适用于任何高性能应用。

功能

2.5V±0.2V电源为DDR400/333

时钟频率高达200 MHz;双数据速率架构;每个时钟周期两次数据传输

差分时钟输入(CLK和CLK)

DQS与Read的数据边对齐;与用于写入的数据居中对齐

CAS时延:2、2.5和3

爆发长度:2,4和8

自动刷新和自我刷新

预充电下电和有源下电_写数据掩码

写时延= 1

15.6µS刷新间隔(4K/ 64ms刷新)

最大突发刷新周期:8

接口:SSTL_2

TSOP II 66针封装,使用符合RoHS标准的无铅材料

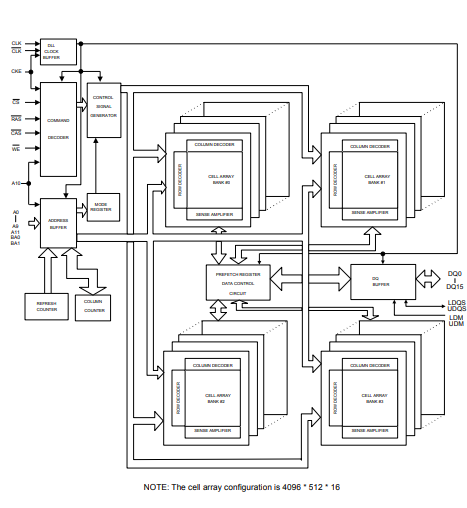

框图